## Position Paper CB24I

# Classification of Binary 24 V Interfaces - Functional Safety aspects covered by dynamic testing

Edition 2.0.1

## Content

| •     |                                                                                         |    |

|-------|-----------------------------------------------------------------------------------------|----|

|       | List of figures                                                                         | 3  |

|       | List of tables                                                                          | 3  |

| 1     | Scope and purpose of this document                                                      | 4  |

| 2     | Normative references                                                                    | 4  |

| 3     | Terms and definitions                                                                   | 4  |

| 3.1   | Information source (source)                                                             | 4  |

| 3.2   | Information sink (sink)                                                                 | 4  |

| 3.3   | Test pulse generation (TG)                                                              | 4  |

| 3.4   | Test pulse evaluation (TE)                                                              | 4  |

| 3.5   | Supply voltage                                                                          | 4  |

| 3.6   | Test pulse                                                                              | 5  |

| 3.7   | Test pulse duration <b>t</b> i                                                          | 5  |

| 3.8   | Test pulse interval <i>T</i>                                                            | 5  |

| 3.9   | Test pulse delay $\Delta t_i$                                                           | 5  |

| 3.10  | Test pulse phase shift $\Delta t_c$                                                     | 5  |

| 3.11  | ON state                                                                                | 5  |

| 3.12  | OFF state                                                                               | 5  |

| 3.13  | Interface type                                                                          | 5  |

| 3.14  | Class                                                                                   | 5  |

| 3.15  | Output current In                                                                       | 5  |

| 3.16  | Leakage current I <sub>Leakage</sub>                                                    | 5  |

| 3.17  | Load capacitance CL                                                                     | 5  |

| 3.18  | Inductive load L                                                                        | 5  |

| 4     | Minimum information on compatibility to be provided in the manufacturer's documentation | 6  |

| 4.1   | Purpose                                                                                 | 6  |

| 4.2   | Basic electrical parameters                                                             | 6  |

| 4.3   | Structure of the identifying key                                                        | 6  |

| 5     | Characteristics of interface types                                                      | 8  |

| 5.1   | Interface type A                                                                        | 8  |

| 5.1.1 | Static characteristics of interface type A                                              | 8  |

| 5.1.2 | Dynamic characteristics of interface type A                                             | 8  |

| 5.1.3 | Product information to be supplied by the manufacturer                                  | 9  |

| 5.1.4 | Application notes                                                                       | 9  |

| 5.2   | Interface type B                                                                        | 10 |

| 5.2.1 | Static characteristics of interface type B                                              | 10 |

| 5.2.2 | Dynamic characteristics of interface type B                                             | 10 |

| 5.2.3 | Product information to be supplied by the manufacturer                                  | 12 |

| 5.2.4 | Application notes                                                                       | 12 |

| 5.3   | Interface type C                                        | 13 |

|-------|---------------------------------------------------------|----|

| 5.3.1 | Static characteristics of interface type C              | 14 |

| 5.3.2 | Dynamic characteristics of interface type C             | 14 |

| 5.3.3 | Classification of interface type C (and D)              | 15 |

| 5.3.4 | Product information to be supplied by the manufacturer  | 16 |

| 5.3.5 | Application note                                        | 17 |

| 5.4   | Interface type D                                        | 17 |

| 5.4.1 | Static characteristics of a source of interface type D  | 18 |

| 5.4.2 | Dynamic characteristics of a source of interface type D | 18 |

| 5.4.3 | Product information to be supplied by the manufacturer  | 19 |

| 5.4.4 | Static characteristics of a sink of interface type D    | 19 |

| 5.4.5 | Dynamic characteristics of a sink of interface type D   | 19 |

| 5.4.6 | Product information to be supplied by the manufacturer  | 20 |

| 01.10 | r roddol information to be supplied by the manufacturer | 20 |

## List of figures

| Figure 5.1-1: Interface type A                                                          | 8  |

|-----------------------------------------------------------------------------------------|----|

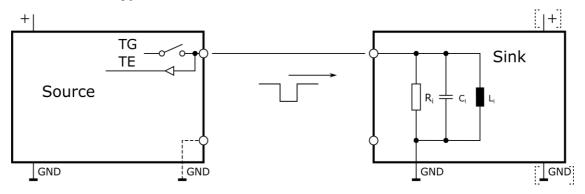

| Figure 5.2-1: Interface type B                                                          | 10 |

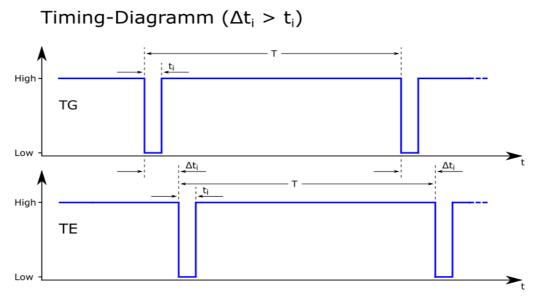

| Figure 5.2-2: Test pulse delay $\Delta t_i$ much smaller than test pulse duration $t_i$ | 11 |

| Figure 5.2-3: Test pulse delay $\Delta t_i$ greater than test pulse delay $t_i$         | 11 |

| Figure 5.3-1: Interface type C                                                          | 13 |

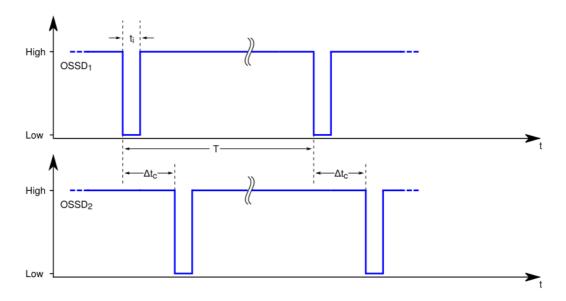

| Figure 5.3-2: Dynamic behaviour interface type C                                        | 15 |

| Figure 5.4-1: Interface type D                                                          | 17 |

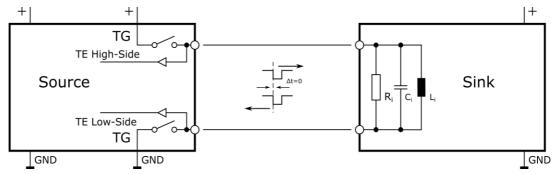

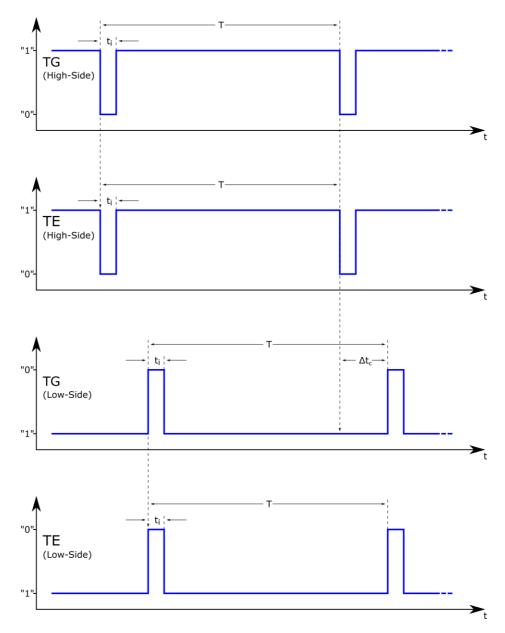

| Figure 5.4-2: Dynamic behaviour interface type D                                        | 18 |

## List of tables

| Table 4.2-1: Basic electrical parameters                        | 6  |

|-----------------------------------------------------------------|----|

| Table 5.1-1: Manufacturer information interface type A – Source | 9  |

| Table 5.1-2: Manufacturer information interface type A – Sink   | 9  |

| Table 5.2-1: Manufacturer information interface type B – Source | 12 |

| Table 5.2-2: Manufacturer information interface type B – Sink   | 12 |

| Table 5.3-1: Classification for interface type C (and D)        | 15 |

| Table 5.3-2: Manufacturer information interface type C – Source | 16 |

| Table 5.3-3: Manufacturer information interface type C – Sink   | 16 |

| Table 5.4-1: Manufacturer information interface type D – Source | 19 |

| Table 5.4-2: Manufacturer information interface type D – Sink   | 20 |

## 1. Scope and purpose of this document

This document describes characteristic features of binary 24V interfaces that use dynamic test pulses.

The purpose of this document is to:

- describe terms and definitions;

- define characteristics of interface types;

- specify product information (technical data) per interface type to be supplied by the manufacturer.

This document provides a technical description for all interface types. No safety-related assessment is made.

## 2. Normative references

This document refers to additional technical documentation and standards. Please note that references to documents with release dates are limited to this version only. For all other documents, the reference is linked to the latest version (including any amendments).

The general requirements set out in IEC 61131-2:2007 shall apply with respect to the present document where reference is made to them.

## 3. Terms and definitions

Section 3 of IEC 61131-2:2007 applies in conjunction with the following additions:

## 3.1 Information source (source)

The information source (hereafter referred to as source) is transmitting information to the information sink. The source output is connected to the input of the sink. A source can meet requirements of several interface types at the same time.

Note: For example, the source could be a sensor and the sink a control system. The term refers to the generation of the information and not to the generation of the test pulses. Generation of test pulses can be located in different parts of the system, depending on the interface type.

## 3.2 Information sink (sink)

The information sink (hereafter referred to as sink) is receiving information from the information source. The sink input is connected to the output of the source. A sink can meet requirements of several interface types at the same time.

Note: For example, the sink could be a control system. The term refers to the analysis of the information and not to the analysis of the test pulses. Analysis of test pulses can be located in different parts of the system, depending on the interface type.

## 3.3 Test pulse generation (TG)

Part of the system that generates test pulses used for system diagnosis.

## 3.4 Test pulse evaluation (TE)

Part of the system that evaluates test pulses for system diagnosis.

## 3.5 Supply voltage

Supply voltage is the voltage continuously supplied to a device.

## 3.6 Test pulse

A test pulse is a temporary change of a signal voltage level used to verify the proper operation of the output or device or the transmission path.

## 3.7 Test pulse duration *t<sub>i</sub>*

The test pulse duration  $t_i$  is the time from the start of the test pulse (e.g. falling edge) until the end of the test pulse (e.g. rising edge).

## 3.8 Test pulse interval *T*

The test pulse interval is the time between the start of a test pulse and the start of the next test pulse on the same output.

## **3.9** Test pulse delay $\Delta t_i$

The test pulse delay  $\Delta t_i$  is a pulse delay introduced by the source, between the input and the output of the information source.

## 3.10 Test pulse phase shift $\Delta t_c$

Time shift of test pulses between different test generation channels (interface type C and interface type D).

## 3.11 ON state

The ON state of a source is the state in which the source output supplies energy.

#### 3.12 OFF state

The OFF state of a source is the de-energised state.

## 3.13 Interface type

The interface type is a standardised interface for transmitters of signals (sources) and receivers of signals (sinks). Generation and analysis of test pulses is specified per interface type.

## 3.14 Class

The class is a group of sources and sinks with compatible technical data within an interface type based on the test pulses in use.

#### 3.15 Output current $I_n$

The output current  $I_n$  is the nominal ON state current of an output.

## 3.16 Leakage current *I*<sub>Leakage</sub>

The leakage current *I*<sub>Leakage</sub> is the remaining current of an output for a source or sink in the OFF state.

## 3.17 Load capacitance C<sub>L</sub>

The load capacitance  $C_L$  is the capacitance connected to an electrical output.

## 3.18 Inductive load L<sub>L</sub>

The inductive load  $L_L$  is the inductance connected to an electrical output.

## 4 Minimum information on compatibility to be provided in the manufacturer's documentation

## 4.1 Purpose

To simplify the compatibility check of device interfaces additional information shall be provided in the manufacturers' device documentation.

## 4.2 Basic electrical parameters

These parameters are the basis for the information provided in the manufacturer's documentation.

| Interface<br>type | Maximum electrical resistance of connection cable | Maximum capacitive load of test<br>pulse generation TG<br>(cable <sup>*1</sup> + input capacitance) |

|-------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| А                 | 100 Ω                                             | 20 nF *2                                                                                            |

| в                 | 100 Ω                                             | 20 nF *2                                                                                            |

| С                 | 100 Ω                                             | 20 nF                                                                                               |

| D                 | 100 Ω                                             | 20 nF                                                                                               |

\*1 e.g. cable 0.34 mm<sup>2</sup> 5 wires: 60  $\Omega$ /km per single wire, 120 nF/km

\*2 Serial connection to be taken in account.

Table 4.2-1: Basic electrical parameters

## 4.3 Structure of the identifying key

The identifying key has the following structure:

| Source /<br>Sink | Interface type<br>(and class) | Additional<br>measures<br>"M" | Sink /<br>Source | Suitable<br>interface type<br>(and class) | Suitable<br>interface type<br>(and class) | Suitable<br>interface type<br>(and class) |

|------------------|-------------------------------|-------------------------------|------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|

|------------------|-------------------------------|-------------------------------|------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|

- First position is the classification of the product.

- Next, the interface types suitable for this product are specified. Up to three interface types can be indicated.

- If additional measures are required, this is indicated by the letter "M" in the field "Additional measures". Definition of additional measures shall be provided in the manufacturer's documentation.

- A row can only contain interface types of the same kind.

- For products with multiple possible interface types, all possible combinations shall be indicated using several identifying keys.

- The number of cells and the structure of the identifying key are fixed.

## **Examples:**

a) Manufacturer information for a source of interface type C class 2 (e.g. sensor...):

| Source: | C2 |  | Sink: | C1 | C2 |  |

|---------|----|--|-------|----|----|--|

|---------|----|--|-------|----|----|--|

Explanation: In this case, a source of type C2 is compatible with a sink of type C1 and also with a sink of type C2.

## b) Manufacturer information for a sink of interface type C class 2 (e.g. safety PLC...):

| Sink: | C2 |  | Source: |  | C2 | C3 |  |

|-------|----|--|---------|--|----|----|--|

|-------|----|--|---------|--|----|----|--|

Explanation: In this case, a sink of type C2 is compatible with a source of type C2 and also with a sink of type C3.

## c) Manufacturer information for a sink of interface type A (e.g. safety evaluation unit...):

| Sink: A M Source: | Α |  |  |  |

|-------------------|---|--|--|--|

|-------------------|---|--|--|--|

Explanation: In this case, a sink of type A is compatible with a source of type A subject to the additional measures "M".

Note: For the free classes C0 and D0, the identifying key is not used. These interface types require an individual compatibility test.

## 5 Characteristics of interface types

## 5.1 Interface type A

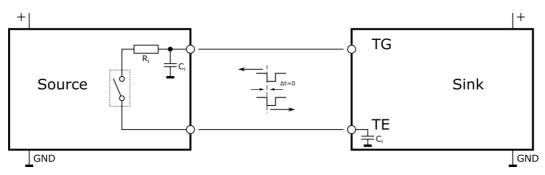

Figure 5.1-1: Interface type A

## **Description:**

A sink sends test pulses to a source. The test pulses are returned to the sink without any change. If the sink does not receive test pulses the sink will enter a safe state. Cascading (series connection) of several sources is supported by this interface type. Internal resistances  $R_i$  of sources connected in series are additive. This needs to be taken into account when determining the expected value for the input voltage at the sink.

## Examples:

Magnetically operated position sensors and limit switches (Reed switches) on hydraulic and pneumatic cylinders.Examples of sinks specific to this interface type are electronic control systems.

## 5.1.1 Static characteristics of interface type A

- An interface of a type A sink has an output for test pulse generation (TG). In addition, the sink has an input for test pulse evaluation (TE)

- An interface of a type A source has a signal input for a test pulse and a signal output for instantaneous output of the test pulse.

- The electrical data shall be based on IEC 61131-2:2007 and will not be further addressed here. Sources of type A can be connected in series and allow potential-free operation.

## 5.1.2 Dynamic characteristics of interface type A

- If information is passed on by a source of type A, no test pulse delay to the output signal occurs.

- An interface of a type A source does not impose any requirement to timing characteristics of the test pulse. The source does not initiate a test pulse at the output on its own. In the OFF state of the source, test pulses are not passed on.

## 5.1.3 Product information to be supplied by the manufacturer

The user manual of a type A source interface shall provide additional data as follows:

| Parameter/Source                                                     | min.                                      | typ.   | max.                                             |

|----------------------------------------------------------------------|-------------------------------------------|--------|--------------------------------------------------|

| Switching current <i>I</i> i                                         | Minimum current <b>I</b> i min            | -      | Maximum current <b>l</b> i max                   |

| Switching voltage <b>U</b> i                                         | Minimum voltage <b>U</b> i min            | -      | -                                                |

| Internal resistance <b>R</b> <sub>i</sub><br>(in the switched state) | Minimum internal resistance <b>R</b> imin | -      | Maximum internal resistance<br><b>R</b> i max    |

| Load capacitance CL                                                  | -                                         | -      | Maximum capacitance at the output <b>C</b> L max |

| Load inductance <i>L</i> L                                           | -                                         | -      | Maximum inductance at the output <b>L</b> L max  |

| Potential-free                                                       |                                           | yes/no |                                                  |

Table 5.1-1: Manufacturer information interface type A - Source

The user manual of a type A sink shall provide additional data as follows:

| Parameter/Sink                               | min.                                      | typ. | max.                                            |

|----------------------------------------------|-------------------------------------------|------|-------------------------------------------------|

| Input current <i>li</i><br>(in the ON state) | Minimum current <b>l</b> i <sub>min</sub> | -    | Maximum current <b>I</b> i <sub>max</sub>       |

| Output voltage <b>U</b> i                    | Minimum voltage <b>U</b> i min            | -    | Maximum voltage <b>U</b> i max                  |

| Input capacitance Ci                         | -                                         | -    | Maximum capacitance at the input <b>C</b> i max |

Table 5.1-2: Manufacturer information interface type A – Sink

## 5.1.4 Application notes

If multiple sources of type A are connected in series, the total voltage drop has to be considered.

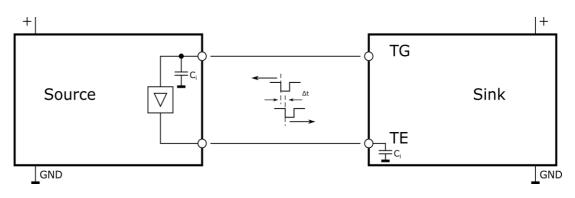

## 5.2 Interface type B

Figure 5.2-1: Interface type B

## **Description:**

A sink generates periodic test pulses with a test pulse interval **T**. The periodic test pulses are delayed by the source by the time  $\Delta t_i$  and returned to the sink without other modification. If the test signals are not passed on to the sink by the source, or if the expected time value of the sink is outside the permissible tolerance limits, the sink will enter a safe state. This interface type allows cascading (series connection) of sources. Test pulse delays  $\Delta t_i$  of sources connected in series are additive. This needs to be taken into account when determining the expected time value for the sink.

## **Examples:**

Interface type B is often used for position monitoring with sensors (source) of different technologies (inductive / RFID / magnetic / photoelectric / etc.) thanks to its ability for series connection. Examples of sinks specific to this interface type are electronic evaluation units and electronic control systems.

## 5.2.1 Static characteristics of interface type B

- An interface of a type B sink has an output for test pulse generation (TG). In addition, the sink has an input for test pulse evaluation (TE).

- An interface of a type B source has an input for the signal of the test pulse generation (TG) and an output for the delayed test signal.

- The electrical data shall be based on IEC 61131-2:2007 and will not be further addressed here. All signals of this interface type are referenced to the signal ground (GND).

## 5.2.2 Dynamic characteristics of interface type B

- Two versions of interface type B exist:

- 1) The test pulse delay  $\Delta t_i$  is much smaller than the test pulse duration  $t_i$  (see figure 5.2-2).

- 2) The test pulse delay  $\Delta t_i$  is greater than the pulse duration  $t_i$  (see figure 5.2-3).

Figure 5.2-2: Test pulse delay  $\Delta t_i$  much smaller than test pulse duration  $t_i$

Figure 5.2-3: Test pulse delay  $\Delta t_i$  greater than test pulse delay  $t_i$

The length of the test pulse duration  $t_i$  is determined by the sink. If the signal shape (pulse/pause ratio, delay) at the input of the sink is in the expected range, the sink can adopt a release state with regard to the source. If the signal shape does not correspond to the expected time value or if no signal is present, no release occurs in the sink. A "no release" on the part of the source means that no signal is transmitted to the sink.

The falling edge and the rising edge of the test input signal of the sink both occur with a test pulse delay of  $\Delta t_i$  at the output of the source. The test pulse delay  $\Delta t_i$  is a deliberately introduced delay time, which clearly differs from parasitic delay times. Typically, the switch-on and switch-off times of the test pulses including their tolerances are much smaller than the test pulse duration  $t_i$ .

The timing characteristics of the test pulse generation (TG) are influenced by the capacitive load of the source ( $C_i$ ) and have an effect on the total time. Furthermore, the input capacitance ( $C_i$ ) of the sink influences the timing aspects of the test pulse analysis. Knowing the size of this capacitance ( $C_i$ ) is essential for users of interface type B.

It is recommended that the capacitive, inductive and resistive parts of the lines (see 5.2-1) between the sink and the source are taken into account. They have an influence on the signal quality but this will not be further taken into account.

## 5.2.3 **Product information to be supplied by the manufacturer**

The user manual of a type B source interface shall provide additional data as follows:

| Parameter                                 | min.                                                | typ. | max.                                                |

|-------------------------------------------|-----------------------------------------------------|------|-----------------------------------------------------|

| Test pulse delay $\Delta t_i$             | Minimum test pulse delay $\Delta t_{i\_min}$        | -    | Maximum test pulse delay $\Delta t_{i\_max}$        |

| Test pulse duration <i>t</i> <sub>i</sub> | Minimum test pulse duration $\Delta t_{i\_min}$     | -    | Maximum test pulse duration $\Delta t_{i\_max}$     |

| Test pulse interval <b>T</b>              | Minimum test pulse interval <b>T</b> <sub>min</sub> | -    | Maximum test pulse interval <b>T</b> <sub>max</sub> |

| Input capacitance <b>C</b> <sub>i</sub>   | -                                                   | -    | Maximum input capacitance $C_{i\_max}$              |

Table 5.2-1: Manufacturer information interface type B – source.

The user manual of a type B sink shall provide additional data as follows:

| Parameter                                | min.                                                | typ. | max.                                                |

|------------------------------------------|-----------------------------------------------------|------|-----------------------------------------------------|

| Test pulse delay $\Delta t_i$            | Minimum test pulse delay $\Delta t_{i\_min}$        | -    | Maximum test pulse delay $\Delta t_{i\_max}$        |

| Test pulse duration <i>t<sub>i</sub></i> | Minimum test pulse duration $\Delta t_i$            | -    | Maximum test pulse duration $\Delta t_i$            |

| Test pulse interval <b>7</b>             | Minimum test pulse interval <b>T</b> <sub>min</sub> | -    | Maximum test pulse interval <b>T</b> <sub>max</sub> |

| Input capacitance <i>C</i> <sub>i</sub>  | -                                                   | -    | Maximum input capacitance <b>C</b> <sub>i_max</sub> |

Table 5.2-2: Manufacturer information interface type B – Sink

## 5.2.4 Application notes

To verify the correct combination of signal sources (e.g. sensors in a plant) and signal sinks (e.g. secondary control system), proceed as follows:

- Verification of interface types:

- Source and sink shall be of interface type B.

- Verification of time parameters:

- Comparison of the test pulse interval T (min. / max.) of the sink with that of the source. The permissible test pulse interval T of the source shall be in the specified range of the sink.

- Comparison of the permissible (min. / max.) test pulse duration  $t_i$  of the source with that of the sink. Ideally, the test pulse duration  $t_i$  of the sink should be slightly smaller than the max. permissible test pulse duration of the source. The minimum required test pulse duration  $t_i$  of the source shall be considered.

• The test pulse delay  $\Delta t_i$  of the source shall correspond to the permissible test pulse delay  $\Delta t_i$  of the sink.

Test pulse delays  $\Delta t_i$  of sources connected in series are additive. The test pulse delay  $\Delta t_i$  monitoring allows e.g. detection of wrong wiring as one of the benefits.

## 5.3 Interface type C

Figure 5.3-1: Interface type C

## **Description:**

A source switches the supply voltage to the output in the ON state. In the OFF state, the output is disconnected from the supply voltage.

In the ON state, the source transmits test pulses to the output. The correct function of the output is monitored in the source itself.

The sink shall suppress the test pulses of the source to prevent unintentional switching operations. The test pulse generation in the source, the test pulse transmission on the line and the input circuit of the sink shall be matched to avoid an unintended shutdown.

The interface type C source itself detects failures of the output switching unit (e.g. in case of a stuck-at-fault).

## **Examples:**

Interface type C is used as an "OSSD" output (<u>O</u>utput <u>Signal Switching Device</u>) – e.g. safety outputs for light grids and proximity switches with defined behaviour under fault conditions as per EN 60947-5-3 etc. The devices, as a source, check the function of their outputs with test pulses. The sink, e.g. control systems, relays or valves, shall not react to these test pulses. If devices have a sink and a source, series connections of devices are possible. Interface type C is, therefore, often used for position monitoring.

## Classes:

Sources of interface type C are subdivided in classes according to the timing characteristics of the test pulses. When combining a source and a sink, it shall be ensured that the source always has the same or a higher class (i.e. shorter test pulses) than the sink (see section 5.3.3).

Note 1: Verification of electric parameters: The limit values of the sink/source shall not be exceeded.

Note 2: The maximum load capacitances and inductances in the input of the sink shall not exceed the maximum values defined in the source. The capacitance and inductance per unit length of the line should be taken into account.

## 5.3.1 Static characteristics of interface type C

- The positive-switching output (P switch) of the source determines the switching status of the system.

- All signals of this interface type are referenced to the signal ground (GND).

- The electrical data for interface type C shall be based on IEC 61131-2:2007 and will not be further addressed here.

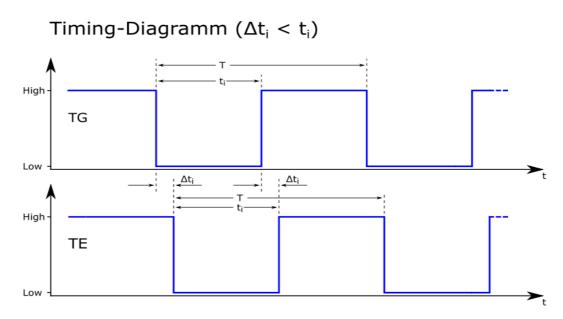

## 5.3.2 Dynamic characteristics of interface type C

## Test pulse duration *t<sub>i</sub>*

- The duration of the test pulses *t<sub>i</sub>* emitted by a source of a certain class shall not exceed the test pulse duration *t<sub>i</sub>* specified in Table 5.3-1. Sinks of a certain class of interface type C shall not react functionally to the test pulses defined for this class as per Table 5.3-1.

- An interruption of the test pulses by the source due to further signal edges (e.g. for data transmission) is permissible. The time from the first switch-off until the last switch-on of the output is considered the test pulse length. A sink shall ignore any such interruptions within a defined test pulse duration.

Note 1: The test pulses shall be filtered out or suppressed in the sink to ensure that no functional influences occur. Flashing or dimming of an illuminated display indicating the input status is tolerated.

Note 2: The timing characteristics of the source's test pulses are influenced by the inductive and capacitive load of the line and the sink. Knowing the size of these values in the sink and the maximum permissible values for a source is essential for users of type C.

It is recommended that the capacitive and inductive parts of the lines between the sink and the source are taken into account as they influence the signal quality. This is not topic of this paper.

## Test pulse interval T

• The test pulse duration  $t_i$  should not exceed 1% of the test pulse interval T. If the test pulse duration is greater than 1% of the test pulse interval, the  $t_i/T$  ratio shall be explicitly mentioned in the technical documentation.

Note: Sinks of a certain class of interface type C shall be designed so that the repeated test pulses in the intervals defined in Table 5.3-1 will not cause an impermissible drop of the energy level in the input (e.g. coils such as relays and valves).

## 5.3.3 Classification of interface type C (and D)

| Parameter           | Designation      | Unit | Value   |         |         |  |

|---------------------|------------------|------|---------|---------|---------|--|

| i arameter          |                  |      | minimum | nominal | maximum |  |

| Class 0 (generic)   |                  |      |         |         |         |  |

| Test pulse duration | <b>t</b> i,0     | μs   | -       |         | free*   |  |

| Class 1             |                  |      |         |         |         |  |

| Test pulse duration | <b>t</b> i,1     | μs   | -       |         | 1000    |  |

| Class 2             |                  |      |         |         |         |  |

| Test pulse duration | <b>t</b> i,2     | μs   | -       |         | 500     |  |

| Class 3             |                  |      |         |         |         |  |

| Test pulse duration | t <sub>i,3</sub> | μs   | -       |         | 100     |  |

\*) to be specified individually for the individual device.

Table 5.3-1: Classification for interface type C (and D)

Figure 5.3-2: Dynamic behaviour interface type C

## 5.3.4 Product information to be supplied by the manufacturer

The user manual of a type C source interface shall provide additional data as follows (see also under 5.3.3):

| Parameter                                | min.                                                     | typ. | max.                                                 |

|------------------------------------------|----------------------------------------------------------|------|------------------------------------------------------|

| Class                                    | Classification according to Table 5.31                   |      |                                                      |

| Test pulse duration ti                   | Minimum test pulse duration <i>t<sub>i_min</sub></i> (*) | -    | Maximum test pulse duration <i>t<sub>i_max</sub></i> |

| Test pulse interval <b>T</b>             | Minimum test pulse interval <i>T<sub>min</sub></i> (**)  | -    |                                                      |

| Nominal current <b>I</b> <sub>N</sub>    | -                                                        | -    | Output current IN                                    |

| Capacitive load <b>C</b> L               | -                                                        | -    | Maximum capacitive load <b>C</b> L_max               |

| Inductive load <i>L</i> <sub>L</sub> (*) | -                                                        | -    | Maximum inductive load <i>L<sub>L_max</sub></i>      |

(\*) = optional supplementary information provided by the manufacturer.

$(^{**})$  = to be indicated by the manufacturer if t/T ratio is greater than 1%.

Table 5.3-2: Manufacturer information interface type C - Source

The user manual of a type C sink shall provide additional data as follows:

| Parameter                                | min.                                                    | typ. | max.                                                     |

|------------------------------------------|---------------------------------------------------------|------|----------------------------------------------------------|

| Class                                    | Classification according to Table 5.31                  |      |                                                          |

| Test pulse duration <i>t</i> i           |                                                         | -    | Maximum test pulse duration <i>t<sub>i_max</sub></i>     |

| Test pulse interval <b>T</b>             | Minimum test pulse interval <i>T<sub>min</sub></i> (**) | -    |                                                          |

| Input resistance <b>R</b>                | Minimum input resistance <b>R</b> L_min                 | -    | -                                                        |

| Capacitive load CL                       | -                                                       | -    | Maximum input capacitive load <b>C</b> <sub>L_max</sub>  |

| Inductive load <i>L</i> <sub>L</sub> (*) | -                                                       | -    | Maximum input<br>inductive load <i>L<sub>L_max</sub></i> |

(\*) = optional supplementary information provided by the manufacturer.

Table 5.3-3: Manufacturer information interface type C – Sink

## 5.3.5 Application notes

To verify the correct combination of signal sources (e.g. sensors in a plant) and signal sinks (e.g. downstream control systems), proceed as follows:

- Verification of interface types: Source and sink shall both be of interface type C.

- Verification of the class: The class of the sink shall correspond to the class of the source.

Note 1: The source shall have the same or a higher class than the sink. For example, a source of class 2 is compatible with a sink of class 1 or 2, but not with a sink of class 3.

Note 2: In the case of a generic source or sink, the manufacturer's specifications shall be compared. The maximum test pulse duration of the source shall not exceed the maximum test pulse duration of the sink.

Note 3: The guaranteed minimum test pulse interval of the source shall be greater than the requested minimum test pulse interval of the sink.

Verification of electric parameters: The load caused by the sink shall not exceed the limits of the source.

Note 4: The output current of the source shall meet the requirements of the input resistance of the sink.

Note 5: The maximum load capacitances and inductances for the input of the sink are those specified in the source. The capacitance and inductance per unit length of the line should be taken into account.

## 5.4 Interface type D

Figure 5.4-1: Interface type D

Interface type D is primarily used for the safe switching of actuators such as contactors, motors and valves, or for complete shut-down of the operating voltage of electric/electronic assemblies and devices. The major difference to the positive-switching output (P switch, see interface type C) is that the return line is also controlled and tested, so that errors in the return line, such as short circuits to 0 V, can be detected. Vagabond voltages due to a shared but floating 0 V connection point will be prevented with this type of connection.

In addition, dual-channel switch-off is possible with 2 lines, preventing impermissible switching of the actuator due to a short circuit on one of the conductors. For this purpose, the source transmits test pulses to the sink. The test pulses are analysed by the source. The test pulses are neither distorted nor delayed by the sink.

The sink can have capacitive, inductive and resistive parts, e.g. actuators such as valves, contactors or drives, but also full devices. The source is typically a safety controller or a safety switching unit with a bipolar output.

## 5.4.1 Static characteristics of a source of interface type D

- The source has a defined impedance, which shall be included in the technical data. The source can switch a load ON and OFF (bipolar, P/N) within a defined output current range.

- ON state is defined as the signal level where the sink reaches its ON state (limit is *I<sub>max</sub>* of the source). OFF state is defined as the signal level where the sink reaches its OFF state (limit is *I<sub>min</sub>* of the source).

## 5.4.2 Dynamic characteristics of a source of interface type D

• Defined test pulses are generated to detect cross faults and short circuits. The test pulse interval and the test pulse duration are to be specified.

Figure 5.4-2: Dynamic behaviour interface type D

• Cyclic testing is causing additional power loss in the source and in the sink. This is based on the dynamic charging and discharging of capacitances and inductances and those values need to be defined for this interface type.

## 5.4.3 Product information to be supplied by the manufacturer

The user manual of a type D source interface shall provide additional data as follows:

| Parameter                                                                 | min.                                                | typ. | max.                                   |

|---------------------------------------------------------------------------|-----------------------------------------------------|------|----------------------------------------|

| Class                                                                     | Classification according to table 5.3-1             |      |                                        |

| Test pulse duration ti                                                    | Minimum test pulse duration <b>t</b> i              | -    | Maximum test pulse duration <b>t</b> i |

| Test pulse interval <b>T</b>                                              | Minimum test pulse interval <b>T</b> <sub>min</sub> | -    | -                                      |

| Leakage current <i>I<sub>Leakage</sub></i> of the output in the OFF state | -                                                   | -    | Maximum output current ILeakage        |

| Nominal current <b>I</b> <sub>N</sub> of the output in the ON state       | -                                                   | -    | Nominal current <b>I</b> N             |

| Capacitive load <b>C</b> L                                                | -                                                   | -    | Maximum capacitive load <b>C</b> L     |

| Inductive load LL                                                         | -                                                   | -    | Maximum inductive load L               |

Table 5.4-1: Manufacturer information interface type D – Source

## 5.4.3.1 Classes

Devices of interface type D are subdivided in classes according to the timing characteristics of the test pulses. When combining a source and a sink, it shall be ensured that the source always has the same or a higher class (i.e. shorter test pulses) than the sink (see Classification of interface type C).

## 5.4.4 Static characteristics of a sink of interface type D

- The sink has a defined impedance which shall be included in the technical data.

- In particular, it shall be ensured that the required minimum current for the ON state and the maximum permissible leakage current for the OFF state can be met by the source.

- The sink shall provide the operating mode "bipolar disconnectable".

## 5.4.5 Dynamic characteristics of a sink of interface type D

- In the event of a bipolar disconnection, the relevant function of the sink shall be deactivated.

- Limits for the test pulse interval and the test pulse duration shall be defined in case the sink is designed to accept test pulses of the source.

- Cyclic testing is causing additional power loss in the source and in the sink. This is based on the dynamic charging and discharging of capacitances and inductances and those values need to be defined for this interface type.

## 5.4.6 Product information to be supplied by the manufacturer

The user manual of a type D sink shall provide additional data as follows:

| Parameter                                  | min.                                                             | typ. | max.                                            |  |

|--------------------------------------------|------------------------------------------------------------------|------|-------------------------------------------------|--|

| Class                                      | Classification according to table 5.3-1                          |      |                                                 |  |

| Test pulse duration t <sub>i</sub>         | -                                                                | -    | Maximum test pulse duration $t_i$ at the input  |  |

| Test pulse interval <b>T</b>               | Minimum test pulse interval <b>T</b> <sub>min</sub> at the input | -    | -                                               |  |

| Input resistance <b>R</b>                  | Minimum input resistance <b>R</b> L                              | -    | -                                               |  |

| Input current <i>Iow</i> in the ON state   | -                                                                | -    | Maximum input current <b>l</b> onmax            |  |

| Input current <i>lorr</i> in the OFF state | -                                                                | -    | Maximum input current <b>I<sub>OFFmax</sub></b> |  |

| Input capacitance CL                       | -                                                                | -    | Maximum input capacitance <b>C</b> L            |  |

| Input inductance L                         | -                                                                | -    | Maximum input inductance <b>L</b> L             |  |

Table 5.4-2: Manufacturer information interface type D – Sink

## 5.4.6.1 Classes

Devices of interface type D are subdivided in classes according to the timing characteristics of the test pulses. When combining a source and a sink, it shall be ensured that the source always has the same or a higher class (i.e. shorter test pulses) than the sink (see Classification of interface type C).

## 5.4.6.2 Application note

In order to ensure the OFF state of the sink, the maximum input current of the sink for the OFF state shall be greater than the maximum leakage current of the source.

## Imprint

Position Paper CB 24 I Classification of binary 24 V Interfaces – Functional Safety aspects covered by dynamic testing

#### Publisher:

ZVEI – German Electrical and Electronic Manufacturers' Association e. V.

Automation Division Lyoner Straße 9 60528 Frankfurt am Main, Germany

Contact: Dr Markus Winzenick Tel. +49 69 6302-426 Email: <u>winzenick@zvei.org</u> www.zvei.org

April 2017

Despite the utmost care, the ZVEI accepts no liability for the content. All rights, in particular those relating to saving, copying, distribution and translation are reserved.