White Paper

## Benchmarking IC Development for Automotive Applications

# Benchmarking Design Implementation Productivity

Complexity Units Automotive Thoughout IC Concept Phase

August 2017 German Electrical and Electronic Manufacturers' Association

## **1** Introduction

The request for individual mobility in our society is constantly rising. Today and probably for the next decade the individual as well as commercial demands for mobility solutions are mainly fulfilled by the automotive industry. New functions like automated driving as well as services e.g. navigation, vehicle to vehicle communication, software upgrades, ..., are enabled by new highly integrated semiconductors which become more and more complex. In parallel development cycles in the automotive industry are getting shorter and costs are facing a high pressure. To stay in this attractive and demanding market for semiconductors, the suppliers need to deal with cost pressure, shortened development cycles and rising quality demands - i.e. just being competitive and being "best in class".

But – what does the wording "best in class" mean? Lowest Cycle Time? Lowest

Cost? Lowest number of silicon design Iterations? This is widely discussed in a white paper by numetrics (1). Each semiconductor company might give one or the other parameter a higher relevance in their key performance indicators (KPI) But for comparison "productivity" and "thoughput" are always relevant for evaluating, if the own company is working in a competitive mode.

It is certainly of interest to measure the parameters "productivity" and "thoughput" on several projects in the own company and to discuss, why the development of some projects performs better compared to others. But it is also of interest to widen the view and to compare the project development performance of the whole semiconductor industry in an integral and neutralised way and to derive out of that some trends for the future.

## 2 Benchmark

Because of that several european semiconductor suppliers under the head of the ZVEI decided to define and to run a regular benchmark survey to compare the product development performance in a neutral way.

This benchmark is running since 2006 and gives some valuable insight based on real project data. For this purpose the benchmarks collects for each project characteristic data as for instance the number of wafer mask layers, the number of digital gates, the number of analogue transistors, since 2016 also the ASIL level, man power, design iterations to get the product in production, etc.

It might be obvious, that an IC with a higher complexity level will need a longer development time and a higher man power, than an IC, what is developed with a lower complexity. At the end the results must be comparable.

The integrated circuits for automotive applications of today are mainly mixed signal ICs. This means, they have analogue and digital design-in one piece of silicon. It is also obvious, that analogue design, simulation, verification requires different efforts in time and man power than a digital design, what is automated in a wide manner.

The participating companies spend quite some effort to describe the complexity level for a given IC, so that at the end the results can be compared. A good indicator – and in – between already confirmed for several years – is the complexity unit (CU), which assigns a weight of 8 digital NAND2 equivalents to an analogue transistor. Thus the total number of complexity units

#### CU = #NAND2 equivalents + 8 x #Analog Transistors

is describing then in a good way the complexity of an IC design project. In general the higher the number of complexity units the higher the efforts needed to execute the project. By using complexity units different mixed signal ICs can be compared in an easy way between each other. In the benchmark we defined 3 ranges for designs based on the Complexity Units. These are "low", "medium" and "high" complexity. The thresholds for these ranges are calculated out of the complexity units of all projects of the benchmark for a given benchmark survey. All the data of the projects provided by the participants is anonymised and processed through a data analysis process. The results enable the participating companies to assess their own performance in terms of productivity and throughput during the development in comparison to other survey participants. The basic calculations are related to numetrics (2).

Each benchmark was made up from at least three different projects from each participating company (3) in the 3 complexity levels giving a total of 20 to 30 projects included into each benchmark run. Data are anonymised by a notary as neutral 3<sup>rd</sup> party and normalised. A predefined statistical analysis is done on the data.

As results the productivity and the throughput depending on IC complexity are given for instance, the influence of the team size or the reusability aspect of given design blocks or test concepts on the productivity is shown in several graphs.

The benchmark provides for instance also an answer on the typical question of the engineering management, how many complexity units can be handled by a project team of a given team size in a given time as an industry standard.

The benchmark further collects reasons for delays and difficulties in the development in categories and also gives reasons for shifts between planning and real achievements in a neutralised manner.

Also trends influencing the complexity on an IC development project and the impact of changes are demonstrated. New requirements like the influence of ISO 26262 functional safety are noticed in the 2016 run as well.

## **3 Results**

The following can show only some typical and representative results out of the development benchmark of 2016.

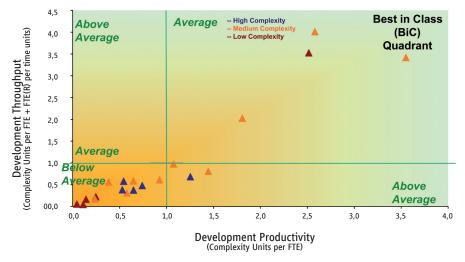

#### Figure 1: Normalised productivity vs. throughput

Source: ZVEI

In a 1<sup>st</sup> conclusion a wide distribution of the projects regarding the development throughput and the development productivity can be seen, some projects perform better than others. Several individual factors for this behaviour will exist in each participating company. As each participant can retrieve out of this graph his own individual company data, internal discussions about the project development performance are possible.

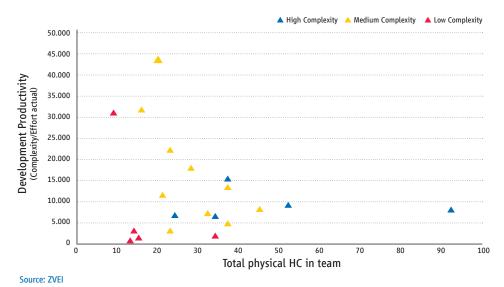

#### Figure 2: Normalised productivity vs. team size

As a general conclusion and in line with the assumptions of numetrics the productivity decreases with growing team size. For the "high" and "medium" complexity projects it is necessary to increase team size to end up with reasonable cycle times. But increasing the team size usually means also increasing management overhead (project structure, team communication, planning overhead, etc.). Individual conclusions must be done then again on individual company level.

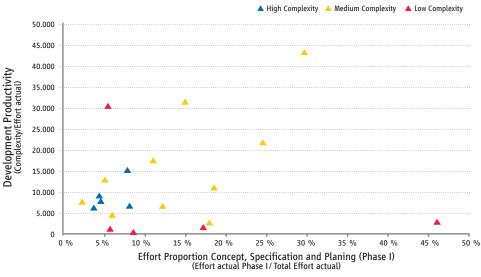

#### Figure 3: Impact of concept phase to the development productivity

Source: ZVEI

A general conclusion for "high" complexity projects is, that the efforts invested in the concept phase, will pay back in improved development productivity. This remark is also valid in general for all the projects, however a bigger distribution can be observed on "medium" and "low" complexity projects, what needs to be discussed again internally in each participating company.

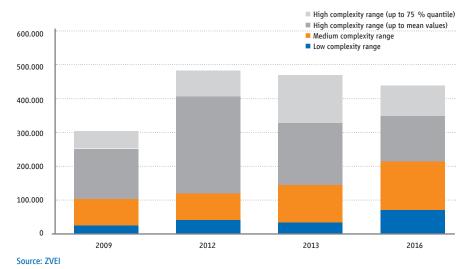

#### Figure 4: Complexity units evaluation over time

The above chart shows the evaluation of the ranges of the complexity units for the "low" and "medium" complexity projects as function of time. For the "high" complexity projects only the evaluation of the mean value and 75 percent quantile are shown in order to remove statistical artefacts. As already mentioned, the number of analogue transistors and NAND2 equivalents in automotive semiconductors significantly increases over the time.

Beside the increase of the complexity units there are also more factors that have an influence on the development throughput and the development productivity:

- On one hand, we see a trend of the ambient temperature range of automotive ICs moving over time to higher values, so that in 2016 in praxis all ICs are in the range of -40 °C...125 °C, the majority of ICs is specified till 150 °C, a 1<sup>st</sup> portion of ICs is already foreseen for >150 °C.

- On the other hand, the semiconductor technologies shrink down to lower feature sizes, the number of used wafer masks increases over time. While in the year 2009 the technology level of all the projects put into this benchmark was on  $\ge 0.35 \ \mu m$  feature size, the benchmark of 2016 shows 50 percent of the projects at a technology level  $\le 0.18 \ \mu m$ .

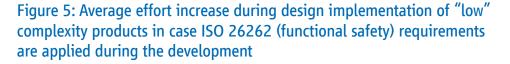

ASIL Level (QM): other

ASIL Level (QM): Application engineers (app note, demo boards, ...)

ASIL Level (QM): Quality engineers

ASIL Level (QM): Product engineers/characterisation (post silicon)

ASIL Level (QM): Test engineers (test program + hardware)

ASIL Level (QM): Layout (Analog as well as place & route)

ASIL Level (QM): Validation pre-silicon/ Verification by independent people

#### Source: ZVEI

A significant effect has the appliance of ISO 26262 (functional safety) to a product development. As this standard is relatively new, certainly also efforts related to methodology developments during the product development are included, so that the dramatic increase of development efforts can be explained and should reduce over time.

The benchmark is highlighting these effects in further analysis results more in detail, so that the participants are able to discuss these results on own company level.

It is obvious that an increased complexity of the automotive semiconductor devices over the years need then higher development efforts in man power and development time. The benchmark provides information of these values, so that the participating companies can take this into account in their project planning for the future.

ASIL Level (QM): Technical project leader(s) / technical leads

ASIL Level (QM): Project management and documentation

ASIL Level (QM): Functional safety management

ASIL Level (QM): Digital designers

ASIL Level (QM): Analog designers ASIL Level (QM): Concept engineers

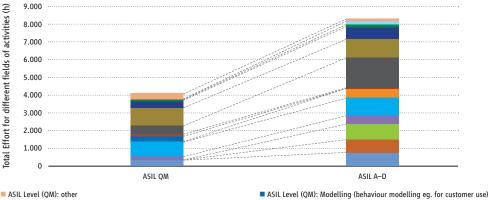

Other elements to be considered are the reasons, what lead to delays during project execution as shown in Figure 6.

#### Figure 6: Reasons for delays in the project development

Source: ZVEI

The analysis shows these reasons for a delay in the project development in percent as well how often a given reason has been mentioned by the participating projects. As technical reason for delay for instance robustness problems towards EMC is mentioned, what usually leads to a redesign of an IC.

But also management problems e.g. lack of resources or frequent requirement changes by customers are highlighted.

Specifically for high complexity projects incomplete presilicon verification and incomplete silicon validation become serious reasons for delays in the project execution.

### 4 Summary

From the results above we can conclude:

- Productivity decreases with increasing complexity of the product. This might as well be an effect of more complex technologies and IC functionality as well as the increase of the team size.

- Team size of complex project must be increased in order to shorten cycle times but simultaneously a decrease of the productivity must be considered by a good compromise.

- The number of complexity units given as number of normalised designs is steadily increasing.

- Several other drivers for complexity increase have been discussed in the benchmark.

- The appliance of ISO 26262 on a product development has a significant influence on development efforts.

With the data of the development benchmark the participating companies are generally enabled to quantify their individual KPI's of IC developments for automotive applications and identify mayor gaps in the development productivity and development throughput as base for improving of design processes, methodology or tooling.

#### Literature

Numetrics, White Paper, 2008, Examining the Criteria for Best-in-Class IC Development Process

Numetrics, White Paper, May 2000, Measuring IC and ASIC Design Productivity

Microchip / Atmel, Elmos, Infineon, Melexis, Robert Bosch, IDT et.all

#### Benchmarking IC Development for Automotive Applications

Published by: German Electrical and Electronic Manufacturers' Association Electronic Components and Systems Division Lyoner Strasse 9 60528 Frankfurt am Main, Germany

Contact: Dr. Sven Baumann Phone: +49 69 6302-468 Fax: +49 69 6302-407 E-mail: baumann@zvei.org

E-mail: baumann@zvei.org Authors: Dr. Hans-Jürgen Brand, IDT Europe Andreas Brüning, Fraunhofer Institute for Integrated Circuits IIS Thomas Freitag, Melexis Dr. Tim Gutheit, Infineon Technologies Armin Kemna, Elmos Semiconductor Hans-Peter Klose, Robert Bosch Benjamin Martini, Infineon Technologies Kristina Rudi, Atmel Automotive Dr. Andreas Vörg, Edacentrum Kai Wacker, Atmel Automotive

www.zvei.org

August 2017

Content in this booklet is licensed under a attribution noncommercial, sharealike, 4.0 international licence.